KAISTは5月6日、チェ・ヤングギュ電気・電子工学部教授とキム・サンヒョン教授の共同研究チームが、既存のCMOSプロセスのみを用いたオシレーター型アイジングマシンの実装に成功したと発表した。オシレーターと結合器をいずれも単一のシリコントランジスタで構成し、代表的な組み合わせ最適化問題であるMax-Cut問題への適用を実証した。

アイジングマシンは、組み合わせ最適化問題を解くための専用計算機だ。組み合わせ最適化問題は、膨大な選択肢の中から最も効率的な解を見つけ出す課題を指し、物流や金融、半導体設計など幅広い分野で重要性が高い。

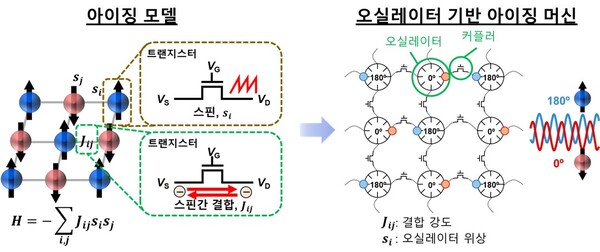

今回の研究では、一定周期で信号を発する振動素子であるオシレーターに着目した。複数のオシレーターが相互に信号をやり取りしながら同期していく過程で、システムが自然に安定状態へ収束し、最適解の探索につながるという考え方だ。

従来のオシレーター型アイジングマシンでは、オシレーター間の微小な周波数差を精密に制御しにくいことに加え、素子同士の接続にも制約があり、実装上の課題となっていた。

これに対し研究チームは、オシレーターと、それらをつなぐ結合器をともに単一のシリコントランジスタで実装する方式を採用した。これにより、オシレーター間の周波数差を抑えて安定した同期を実現したほか、結合強度を多段階で調整できる構成も実装した。

その結果、アイジングモデルの表現力と解探索性能を同時に高められたとしている。研究チームはこの技術を用い、代表的な組み合わせ最適化問題であるMax-Cut問題に適用し、有効性を確認した。

Max-Cut問題は、ネットワークを2つのグループに分けた際、グループ間をつなぐ辺の総和が最大になるよう分割する問題だ。研究チームによると、物流ルートの最適化や金融ポートフォリオの構成、半導体回路の配置などへの応用が期待できるという。

今回の成果の特徴は、特殊材料や非標準プロセスを使わず、現在の半導体産業で広く用いられているCMOSプロセスをそのまま活用した点にある。KAISTは、既存の半導体生産ラインを活用した量産や商用化にもつながる可能性があると説明している。

チェ・ヤングギュ教授は「オシレーターと結合器の両方をシリコン素子で実装することで、拡張性と精密性を同時に確保したアイジングマシンのハードウェアを実現した」とコメントした。その上で「半導体設計自動化や通信ネットワークの最適化、資源配分など、大規模な組み合わせ最適化が求められるさまざまな産業分野への応用が期待される」と述べた。

この研究は韓国研究財団の支援を受けて実施された。ユン・ソンユンKAIST博士課程とキム・ジュンピョ博士が共同筆頭著者として参加しており、論文は3月27日付で「Science Advances」に掲載された。