[디지털투데이 양대규 기자] 삼성전자가 차세대 파운드리 기술인 초미세 3나노 GAA 공정을 구체화했다. 삼성전자에 따르면, 2019년 하반기 4나노 핀펫 공정 개발을 완료할 계획이다. 이후 3나노 공정부터는 GAA 공정을 통해 반도체 칩을 생산한다.

삼성전자는 14일(현지시간) 미국 산타클라라 메리어트 호텔에서 '삼성 파운드리 포럼 2019'를 개최하고 '차세대 3나노 GAA 공정'을 소개했다.

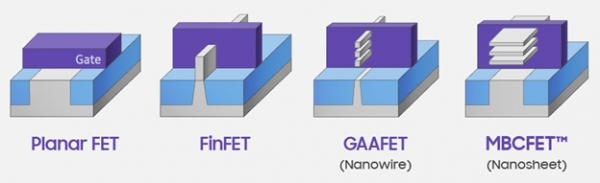

지난해 삼성전자는 GAA(Gate-All-Around)를 3나노 공정에 도입하겠다고 공개했다. 삼성전자는 3나노 GAA 공정을 3GAE(3나노 Gate-All-Around Early)와 3GAP(3나노 Gate-All-Around Plus)나눠, 1세대를 Early, 이후 성능과 전력이 개선된 2세대를 Plus라고 칭했다. 3나노 이전까지의 공정에는 핀펫(FinFET) 구조를 사용한다.

3나노 이하 초미세 회로에 도입될 GAA 구조의 트랜지스터는 모바일, 인공지능(AI), 5G, 전장, 사물인터넷(IoT) 등 고성능과 저전력을 요구하는 차세대 반도체에 적극적으로 활용될 전망이다. GAA 구조는 전류가 흐르는 통로인 원통형 채널(Channel) 전체를 게이트(Gate)가 둘러싸고 있어 3면을 감싸는 지느러미 모양의 핀펫 구조에 비해 전류의 흐름을 더 세밀하게 제어할 수 있다.

삼성전자의 3GAE 공정은 최신 양산 공정인 7나노 핀펫 대비 칩 면적을 45% 가량 줄일 수 있으며, 약 50%의 소비전력 감소와 약 35%의 성능 향상 효과가 기대된다.

삼성전자는 3나노 공정에서 독자적인 MBCFET(Multi Bridge Channel FET) 기술을 통해 차별화된 이점을 팹리스 고객사들에게 제공할 계획이다. MBCFET은 기존의 가늘고 긴 와이어 형태의 GAA 구조를 한층 더 발전시켜 종이처럼 얇고 긴 모양의 나노시트를 적층하는 삼성전자의 독자적인 기술이다. 성능과 전력효율을 높이는 것은 물론 핀펫 공정과도 호환성이 높아 기존 설비와 제조 기술을 활용할 수 있다는 장점을 가지고 있다.

삼성전자는 올해 포럼에서 3GAE의 공정 설계 키트(PDK v0.1, Process Design Kit)를 팹리스 고객들에게 배포했다고 밝혔다. 공정 설계 키트는 파운드리 회사의 제조공정에 최적화된 설계를 지원하는 데이터 파일이다. 이를 활용하면 팹리스 업체가 제품 설계를 보다 쉽게 할 수 있어 시장 출시까지 소요 기간을 단축하고 경쟁력을 높일 수 있다.

삼성전자는 “EUV 노광 기술 기반으로 최근 7나노 제품 양산과 6, 5나노 공정 개발을 완료하며, 초미세 회로 기술을 빠르게 발전시키고 있다"며, “4 나노 핀펫 공정과 3나노 MBCFETTM 공정 개발에도 박차를 가하고 있다”고 설명한다.

삼성전자는 2019년 하반기에 6나노 적용 제품 양산을 시작으로 5나노 기반 제품 회로 설계 완성 그리고 4나노 핀펫 공정을 개발 완료한다는 계획이다. 또한 2020년 상반기에는 5나노 공정 기반 제품을 본격 양산하고, FD-SOI 공정과 eMRAM 그리고 최첨단 패키지 솔루션 확대 등도 계획하고 있다.

SNS 기사보내기

관련기사

- 인텔, 6월 10nm 프로세서 출하…7nm는 2021년?

- 삼성전자, 1분기 영업이익 60%↓…반도체 '부진'·디스플레이 ‘적자’

- TSMC·삼성, ‘파운드리 전쟁’… 6·5nm ‘초미세 공정’으로 이동

- 삼성전자, 2030년까지 시스템 반도체에 133조원 투자

- 글로벌파운드리, 온세미에 300mm IBM 팹 매각

- 삼성전자, 5나노 EUV 공정 개발…이달 중 7나노 출하

- 파운드리2020, 삼성전자는 TSMC를 따라잡을까

- TSMC “2분기 비메모리 시장 회복할 것”

- 삼성전자, 클라우드로 팹리스 설계 지원한다

- ST, 5G 주도로 2021년 14조원 매출 목표

- 삼성전자, ‘새로보다’에서 캐리커쳐 이벤트 진행

- 아두이노, IoT용 새로운 나노 보드 제품군 공개

- 삼성전자·TSMC, 파운드리 미세공정 ‘투자’ 경쟁 ‘치열’

- 글로벌파운드리, ‘아베라 매각’ 이유는 “파운드리 역량 강화”

- 삼성전자, 100W ‘고속 충전’ 전력전달제어 반도체 공개

- 삼성전자, "시스템 반도체 글로벌 1위 달성하겠다"

- '차세대 메모리', 어디까지 개발됐나?

- MRAM·PRAM 등 차세대 메모리 개발, 어떤 기술이 필요할까?

- [심층분석] 차세대 메모리 'MRAM'...단순한 구조로 5G·IoT 장치 적합