韩国研究团队开发出一款可直接基于现有硅半导体工艺实现的计算硬件,面向组合优化问题求解,有望提升相关产业场景的计算效率和准确性。

KAIST 5月6日表示,电气与电子工程系 Choi Yang-gyu 教授与 Kim Sang-hyun 教授联合研究团队,成功利用现有硅半导体工艺实现了用于下一代优化计算的振荡器型 Ising 机器硬件。

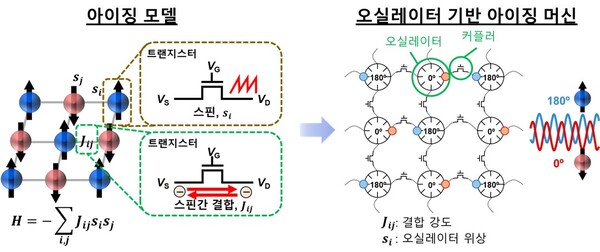

组合优化问题是指在众多可能方案中寻找最优解。Ising 机器则是一类专门用于求解这类问题的计算系统。

研究团队将重点放在振荡器上。振荡器能够周期性产生信号,多个振荡器在相互交换信号并实现同步的过程中,系统会自然趋于稳定状态,并据此找到最优解。团队指出,现有 Ising 机器在精确控制振荡器之间细微频率偏差方面存在局限,器件之间的连接和耦合控制能力也受到限制。

为解决上述问题,研究团队提出了一种新方案:将振荡器及用于连接的耦合器,全部基于单个硅晶体管实现。其中,耦合器负责调节器件之间的相互作用强度。该方案不仅降低了振荡器之间的频率偏差,提升了同步稳定性,还实现了可对耦合强度进行多级调节的多状态耦合。

研究团队表示,这一成果同时提升了 Ising 模型的表达能力和求解性能,并已利用该技术完成典型组合优化问题“最大割(Max-Cut)”的求解验证。所谓最大割,是指将网络划分为两组,并使组间连接最大化,可应用于物流路径优化、金融投资组合优化以及半导体电路布局等场景。

此次研究的一大特点在于,团队未采用特殊材料或非标准工艺,而是直接沿用当前半导体行业广泛使用的互补金属氧化物半导体(CMOS)工艺。CMOS 具备低功耗、低发热等特点,广泛用于智能手机和计算机 CPU 等数字设备制造。KAIST 表示,这项技术有望依托现有半导体生产线实现量产和商业化。

Choi Yang-gyu 表示,此次研究将振荡器和耦合器均构建在硅器件之上,使 Ising 机器硬件在扩展性和精度方面同时得到保障,未来可望应用于半导体设计自动化、通信网络优化、资源分配等需要大规模组合优化的产业领域。

该研究在韩国研究基金会支持下完成,KAIST 博士生 Yun Seong-yun 与 Kim Jun-pyo 博士共同为第一作者,论文已于 3月27日发表于《Science Advances》。