벤처비트에 따르면, 인텔은 15일(현지 시각) 미국 디트로이트에서 열린 국방첨단연구계획국(DARPA) ‘일렉트로닉 리써전스 이니셔티브 2019 서밋’에서 총 800만 개의 뉴런을 시뮬레이션할 수 있는 64칩 컴퓨터 ‘포호이키 비치’ 시스템을 공개했다. 인텔 연구소의 리치 울릭 전무이사는 포호이키 비치가 60개 연구 파트너에게 제공돼 스페어 코딩과 패스 플래닝과 같은 AI 알고리즘을 확장할 수 있을 것이라고 말했다.

울릭은 "우리는 로이히의 규모를 확대하여 보다 강력한 뉴로모픽 시스템을 만들 때 입증된 초기 결과에 깊은 인상을 받았다. 포호이키 비치는 60개 이상의 생태계 파트너들이 이용할 수 있게 될 것이며, 그들은 복잡하고 계산 집약적인 문제를 해결하기 위해 이 특별한 시스템을 사용할 것”이라고 밝혔다.

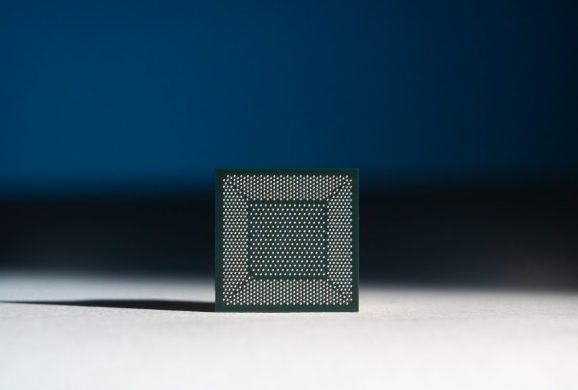

포호이키 비치는 오레곤에서 열린 2018년 NICE(Neuro Inspired Computational Elements) 워크숍에서 128코어, 14나노미터 로이히 뉴로모르핀 칩 64개를 갖추고 있다고 소개됐다. 60mm 다이 크기를 가지고 있으며 20억 개 이상의 트랜지스터, 13만 개의 인공 뉴런, 그리고 1억 3000만 개의 시냅스를 포함하고 있으며, 작업 조정을 위한 3개의 레이크몬트 코어를 관리하고 있다.

벤처비트는 “로이히는 비동기식 스파이크 신경망(SNN)의 칩 훈련을 위한 프로그램 가능한 마이크로코드 학습 엔진을 특징으로 한다. 즉, 모델의 구성요소가 입력 데이터를 동시에 처리하지 않도록 작동 모델에 시간을 통합하는 AI 모델”이라며, “이는 고효율의 적응형 자기 수정, 사건 중심 및 세분화된 병렬 계산의 구현에 사용될 것”이라고 보도했다.

벤처비트에 따르면, 로이히 개발 툴체인에는 로이히 파이썬 API, 컴파일러, 로이히에 SNN을 구축하고 실행하기 위한 런타임 라이브러리 세트로 구성됐다. 그것은 붕괴 시간(decay time), 시냅스 무게, 급상승 임계값(spiking thresholds)과 같은 맞춤형 구성으로 뉴런과 시냅스의 그래프를 만들 수 있는 방법, 그리고 사용자 정의 학습 규칙을 통해 외부 스파이크를 주입함으로써 그 그래프를 시뮬레이션하는 방법을 제공한다.

인텔에 따르면, 로이히는 기존 프로세서에 비해 1000~1만 배 더 효율적으로 정보를 처리하며, 기존 CPU 운용에 비해 속도와 에너지 효율이 3배 이상 높아져 특정 유형의 최적화 문제를 해결할 수 있다. 게다가 인텔은 로이히가 실시간 성능 결과를 유지하고 50배 확대 시 전력 사용량이 30% 증가하는 데 반해 기존 하드웨어는 500% 더 많은 전력을 사용한다고 주장한다. 그리고 이 칩은 널리 사용되는 CPU-런 동시 위치 및 매핑 방식보다 약 100배 적은 에너지를 소비한다고 말한다.

인텔은 올해 말 1억 개 이상의 뉴런을 가진 뉴로모픽 워크로드에 대해 ‘전례가 없는’ 수준의 성능과 효율성을 제공하는 훨씬 더 큰 로이 시스템인 포호키 스프링스를 도입할 것이라고 말한다. 또한 인텔 뉴로모픽 리서치 커뮤니티를 통해 자사의 로이 클라우드 시스템과 로이히에 기반을 둔 USB 폼팩터 시스템인 카포호 베이에 대한 접근을 지속적으로 제공할 것이라고 밝혔다.

SNS 기사보내기

관련기사

- 인텔 "새로운 칩 재료가 AI 대규모 연구 성과 가능하게 할 것"

- 삼성전자, 2030년까지 2천명 투입해 'NPU 기술' 개발한다

- LG전자, AI칩 독자개발…딥러닝 알고리즘 개선

- 인공지능(AI) 시대의 프로세서, 누가 대세?

- AI 웨어러블 링, 심장 모니터링용 '스마트워치' 대체

- MIT, AI 학습이 쉬운 ‘작은 신경망’ 발견

- 삼성전자, 차세대 시스템 반도체 적용 가능한 AI 연구 집중

- 네이버 AI 번역 서비스 '파파고', 월간활성사용자수 1,000만 돌파

- 엔비디아, DIY용 위한 99달러 '젯슨 나노' AI 컴퓨터 공개

- 인텔 ”2021년 7나노 칩 생산할 것”

- 반도체 시장 '무어의 법칙' 유효한가?

- 애플, 인텔 스마트폰 모뎀 사업 '대부분' 인수